Digital Fitler FIR with Variable Coefficients

Description

On Xilinx FPGA.

[IT]

Il presente lavoro riguarda analisi, descrizione e implementazione di un’Architettura FILTRO FIR a Coefficienti Variabili.

Tutte le fasi del Digital Design Flow sono indicate e commentate nel file READ_ME.pdf

Programs Used:

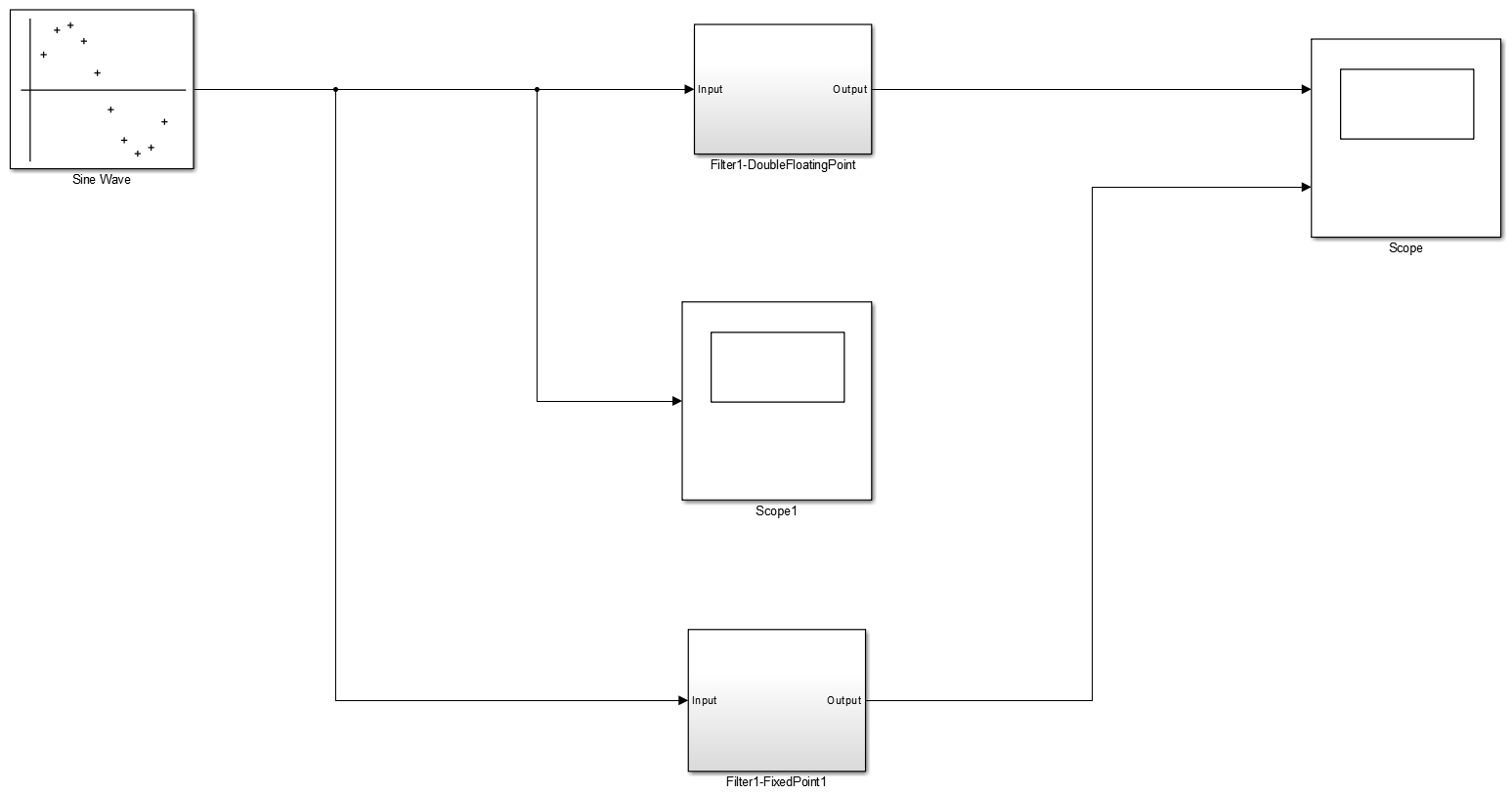

- MATLAB R2014a;

- Simulink;

- Filter Design & Analysis Tool;

- Active-HDL Student Edition;

- Xilinx Vivado Design Suite;

File:

| Allegato | Dimensione |

|---|---|

| 1.74 MB | |

| 3.41 MB |