Low Noise Amplifier @ f = 5.25 GHz in tecnologia AMS S35

Description

[IT]

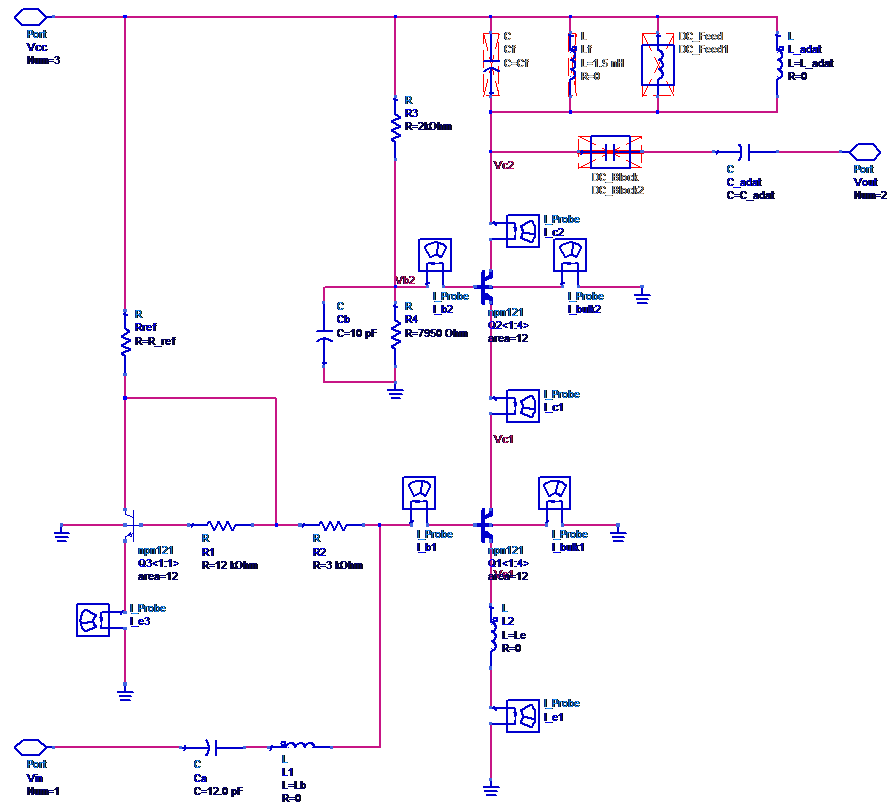

Il presente lavoro riguarda la progettazione e la simulazione di un LNA a transistori bipolari destinato alla fabbricazione col processo AMS S35 0.35um BiCMOS.

Si procede analizzando alcune configurazioni di LNA a singolo stadio di amplificazione in configurazione SE singol transistor, SE cascode e FD cascode, traendo conclusioni sull’efficacia o meno dell’inserimento di un ulteriore stadio di guadagno.

Si dimensiona, infine, l’architettura LNA singolo stadio di amplificazione in configurazione SE cascode con l’utilizzo di induttanze di processo con QS=10.

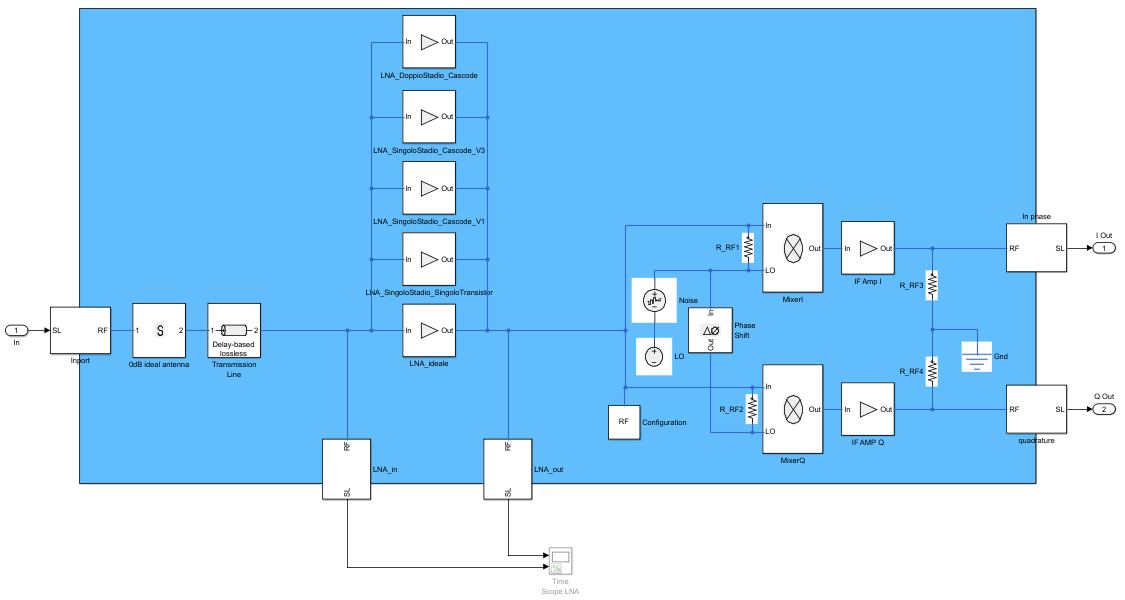

Successivamente si utilizzano i dati derivanti dalla simulazione per la verifica delle prestazioni del progetto all’interno di un sistema ricetrasmettitore per tecnologia 802.11a @ f = 5.25 GHz.

Programs Used:

- Advanced Design System 2009;

- MATLAB R2016b;

| Allegato | Dimensione |

|---|---|

| 2.29 MB |