## OTA (OPERATIONAL TRANSCONDUCTANCE AMPLIFIER) + OUTPUT STAGE SOURCE FOLLOWER.

Di Alessandro Paghi e Lorenzo De Marinis.

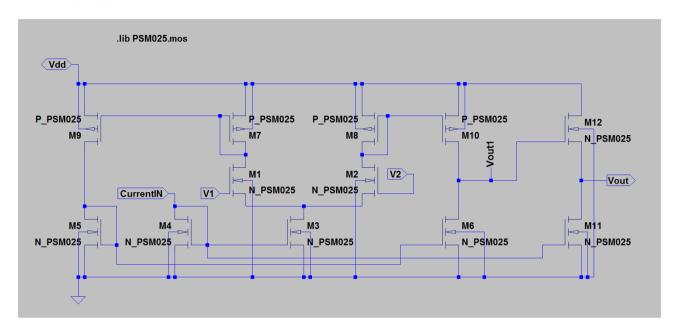

## SCHEMA CIRCUITALE

### SCHEMA SIMBOLICO

### **DIMENSIONAMENTO DEI MOSFET**

### Dati di progetto:

- L = 1 um;

- I\_0 = 10 uA;

- u n\*Cox = 240\*10^(-6) A/V^2;

- u\_p\*Cox = 50\*10^(-6) A/V^2;

- V\_gs-V\_t = 200mV +- 10%;

- V t = 380 mV.

Procedimento per il dimensionamento dei Mosfet:

$$(W/L)_n=2*I_q/[u_n*Cox*(V_gs-V_t)^2]$$

$$(W/L)_p=2*I_q/[u_p*Cox*(V_gs-V_t)^2]$$

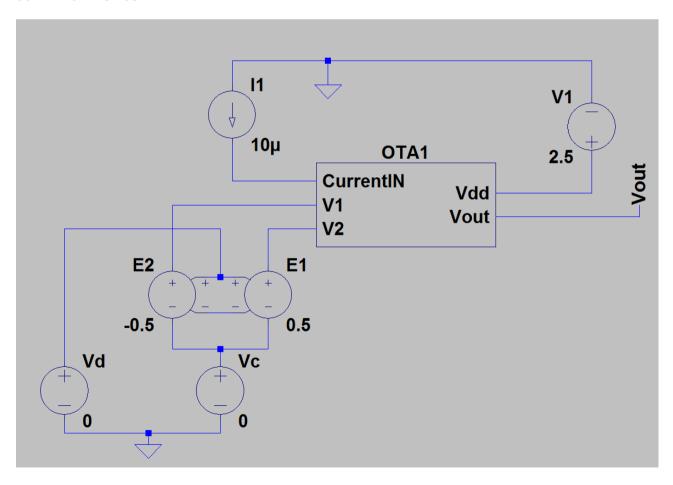

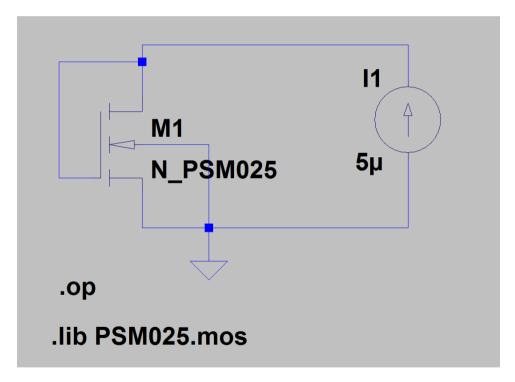

Iterazione dell'operazione di definizione di (W/L) attraverso l'uso del seguente schema circuitale:

(W/L)new = (W/L)old\* $[(V_gs-V_t)$ nominale/ $(V_gs-V_t)$ old]^2

### Per nMOSFET:

- I\_0 = 10uA -> Wn = 3.888 um;

- I\_0/2 = 5uA -> Wn = 1.944 um.

### Per pMOSFET:

•  $I_0/2 = 5uA -> Wp = 9.333 um$ .

#### ANALISI CIRCUITLE A MONTE DELLA SIMULAZIONE

Lo schema circuitale assegnato consiste in uno stato OTA (Operational Transconductance Amplifier) con uno stadio di output del tipo Source Follower.

### Stadio OTA

La soluzione illustrata è una soluzione circuitale adatta ad essere utilizzata con bassi valori delle tensioni di alimentazione.

Chiudendo l'uscita V\_out1 in corto circuito risulta:

- In polarizzazione: I\_OUT1CC = I\_D2-I\_D1;

- Alle variazioni: i\_ucc(t) = g\_mn\*v\_d.

Nello schema assegnato il terminale non invertente è quindi quello contrassegnato con  $V_2$  e quello invertente con  $V_1$ ; per cui risulta  $v_d = v_2 - v_1$ .

La resistenza di uscita R\_out di questo circuito si calcola osservando che dall'uscita vedo solo il parallelo delle resistenze di Drain di M10 e M6, per cui R\_out =  $r_d10//r_d6$ .

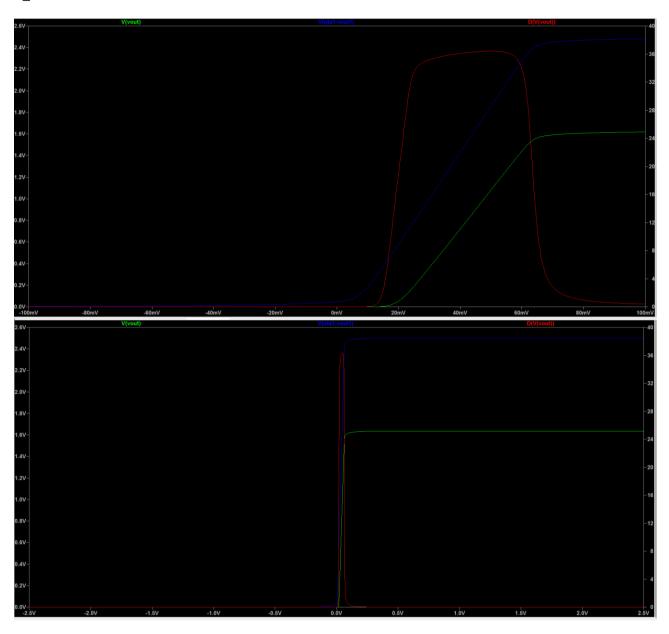

Risulta perciò  $A_d = g_mn*R_out \sim 50$ .

La dinamica di uscita è praticamente estesa dalla V\_ss, che in questo caso è la tensione di riferimento, alla V dd.

L'amplificazione rimane quasi costante per  $V_ss + (V_GS6-V_tn) < V_out1 < V_dd - (|V_GS10|-|V_tp|)$  circa 200 mV <  $V_out1 < 2.3$  mV.

Ci possiamo quindi avvicinare alle tensioni di alimentazioni a meno di una tensione di saturazione  $V_GS-V_t$ .

Oltre questi estremi R\_out decresce diminuisce rapidamente e con essa pure la pendenza della caratteristica, ovvero il guadagno A\_d.

#### Stadio di OUTPUT Source Follower

Per avere un'uscita di tensione è desiderabile una bassa resistenza di uscita in modo da ridurre l'effetto di attenuazione introdotto dall'inserimento di un carico.

Lo stadio di uscita proposto possiede una R\_out = 1/g\_m.

Questa configurazione di output è molto popolare nelle situazioni in cui è presente una tensione di alimentazione di diversi Volt; con la riduzione della tensione di alimentazione, questa semplice configurazione di output non trova più applicazione.

V\_GS11 contiene la tensione di threshold e in aggiunta, in un processo n-well CMOS, il source ed il body di un nMOSFET non sono connessi insieme, perciò V\_t è significativamente aumentata dall'effetto Body.

Ci possiamo aspettare una perdita di circa 1 V.

# SIMULAZIONI

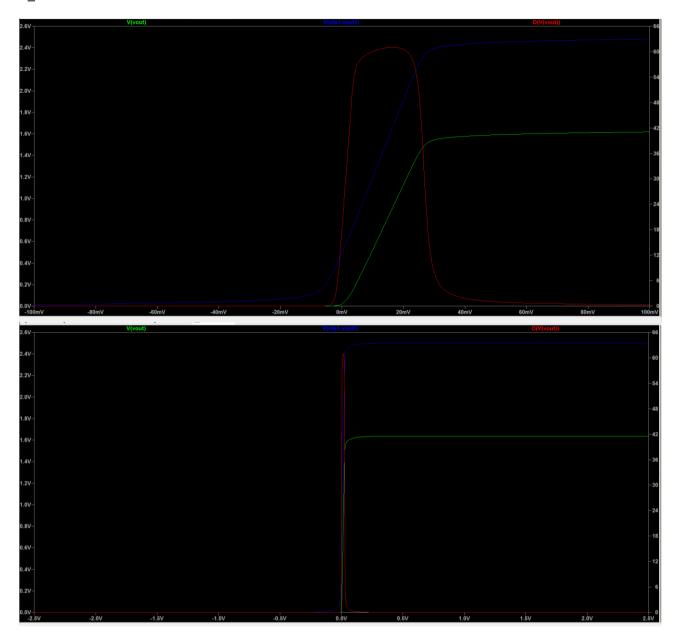

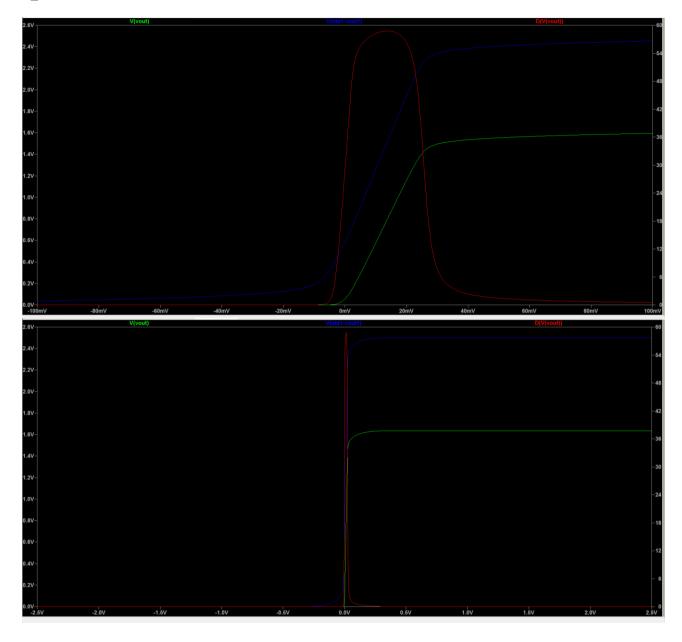

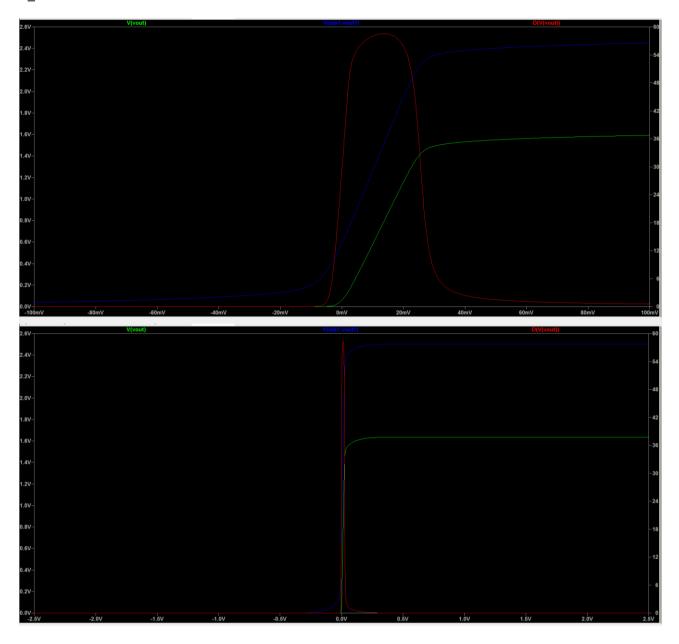

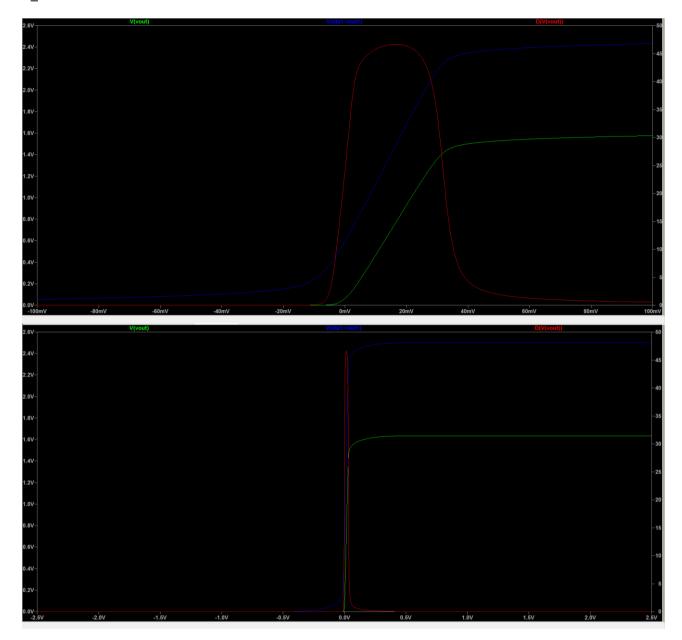

# V\_c = 0 V

I risultati ottenuti dalle simulazioni sono concordi a quanto ipotizzato.

### LTSPICE NETLIST

.lib PSM025.mos .backanno .end

\* C:\Users\Alessandro\Desktop\psm\_work\_OTA14062017\LTSpice\sch-home\DraftSCHEMATIC.asc M1 N001 V1 N004 0 N PSM025 I=1u w=1.944u M2 N002 V2 N004 0 N PSM025 I=1u w=1.944u M3 N004 CurrentIN 0 0 N\_PSM025 I=1u w=3.889u M4 CurrentIN CurrentIN 0 0 N PSM025 I=1u w=3.889u M5 N003 N003 0 0 N PSM025 I=1u w=1.944u M6 Vout1 N003 0 0 N\_PSM025 I=1u w=1.944u M7 N001 N001 Vdd Vdd P\_PSM025 l=1u w=9.333u M8 N002 N002 Vdd Vdd P\_PSM025 I=1u w=9.333u M9 N003 N001 Vdd Vdd P\_PSM025 l=1u w=9.333u M10 Vout1 N002 Vdd Vdd P PSM025 I=1u w=9.333u M11 Vout CurrentIN 0 0 N\_PSM025 l=1u w=3.889u M12 Vdd Vout1 Vout 0 N\_PSM025 I=1u w=3.889u .model NMOS NMOS .model PMOS PMOS .lib C:\Users\Alessandro\Documents\LTspiceXVII\lib\cmp\standard.mos

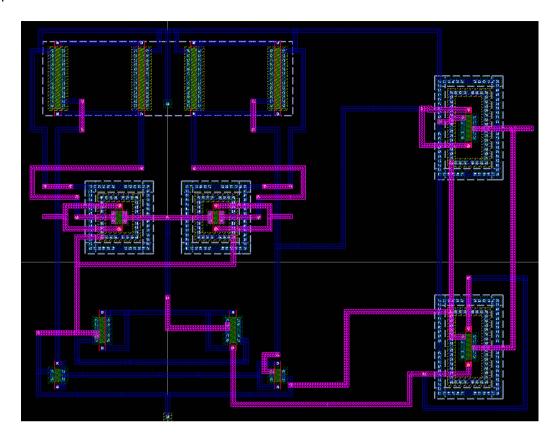

# LAYOUT

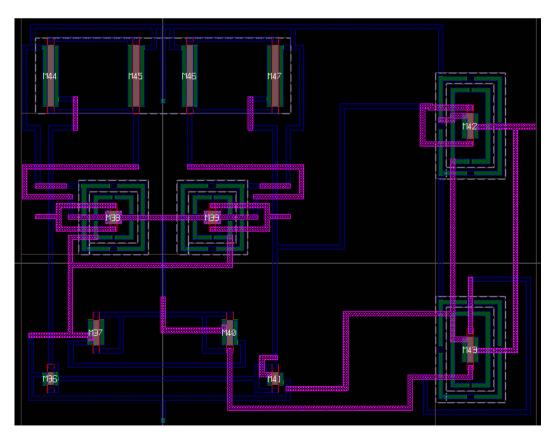

# EXTRACTED

#### **DRC RESULT**

# INFO: Build connectivity graph, 8 tasks

# INFO: Extract connectivity graph...

Check n well

Check active

Check poly

Check p plus

Check n plus

Check contact

Check metal1

Check via

Check metal2

No Errors Detected

### LVS RESULT (Parameter Tollerance 1%)

Gemini 2.7.4 Compiled on Feb 12 2016 at 10:38:27

Graph "C:\Users\Alessandro\Desktop\psm\_work\_OTA14062017\glade\OTA\_extracted.cdl": Number of

devices: 12

Number of nets: 11

Graph "C:\Users\Alessandro\Desktop\psm\_work\_OTA14062017\LTSpice\sch-home\netlist.net": Number of

devices: 12

Number of nets: 11 The circuits are different.

0 size warnings.

13 (56%) matches were found by local matching

All nodes were matched in 9 passes

0 devices and 0 nets written to C:\Users\Alessandro\Desktop\psm\_work\_OTA14062017 -

Copia\glade\OTA.err

### LVS RESULT (Parameter Tollerance 0%)

Gemini 2.7.4 Compiled on Feb 12 2016 at 10:38:27

$Graph "C:\Users\Alessandro\Desktop\psm\_work\_OTA14062017\LTSpice\sch-home\OTA\_extracted.cdl":$

Number of devices: 12 Number of nets: 11

Graph "C:\Users\Alessandro\Desktop\psm\_work\_OTA14062017\LTSpice\sch-home\netlist.net": Number of

devices: 12

Number of nets: 11 The circuits are different.

The following transistors do not match in size:

$7\LTSpice\sch-home\OTA\_extracted.cdl: 4062017\LTSpice\sch-home\netlist.net$

(1) Device type n name1 MM7 name2: M11

s,d: n2 n8: 0 Vout

g: n6 l/w: 1.000/3.889 : CurrentIN l/w: 1.000/3.889

(2) Device type n name1 MM4 name2: M3

s,d: n7 n2: N004 0

g: n6 l/w: 1.000/3.889 : CurrentlN l/w: 1.000/3.889

(3) Device type n name1 MM6 name2: M12

s,d: n0 n8: Vdd Vout

g: n1 l/w: 1.000/3.889 : Vout1 l/w: 1.000/3.889

(4) Device type n name1 MM1 name2: M4

s,d: n2 n6 : 0 CurrentIN

g: n6 l/w: 1.000/3.889 : CurrentIN l/w: 1.000/3.889

4 size warnings.

13 (56%) matches were found by local matching

All nodes were matched in 9 passes

4 devices and 0 nets written to C:\Users\Alessandro\Desktop\psm\_work\_OTA14062017\LTSpice\sch-

$home \verb|\OTA.err|$